10 years ago my friend Ian Lesnet designed the BusPirate. A versatile Swiss army knife that helps you explore serial protocols like SPI, I2C and UART through a simple serial terminal. It was based on a 16 bit Microchip PIC micro controller which features a few clever tricks to make it tick:

- SPI, I2C and UART implemented in silicon

- Peripheral Pin Select (route hardware functions to any pin)

- 5v tolerant pins

- opendrain capable IO pins

- Lots of hardware enabled peripherals

- Thorough accessible datasheet.

He went through a couple of hardware revisions and the final (which is sold as version 3) has a seperate USB to serial convertor and a Microchip PIC microcontroller with 64KB flash and 8KB SRAM. Unfortunately there was also a silicon bug in some of the earlier BusPirates (let’s say the first couple of hundred units sold) with the I2C peripheral which prohibits proper I2C communications. Unfortunately software only implementation proved the best way to avoid users complaining about I2C (but the software implementation too)

The initial firmware went through a couple of revisions of which I laid the basis of a more modular firmware (project newterm). This enables extra features as easily integrate a new protocols and a rudimentary scripting language. I also rewrote the bootloader and messaging system to make maximal use of the available flash space. At some point the firmware (version 6) was hitting the boundries of the chip and we didn’t got any room to add more stuff.

Ian and I tried to move the USB side of things inside the PIC chip itself and we came up with BusPirate Version 4. This one never got off well, since the handling of the USB protocol did interfere with the protocol handling. This resulted into a flaky user experience. However we still thought handling the USB in a separate chip is soo 1980 (so to speak) and released the thing as version 4.

2 Years ago we picked up the gauntlet and tried to migrate the existing code base to a more capable and more future proof microcontroller. We decided to use the quite popular and bang-for-buck STM32F1 series. A USB capable microcontroller based on ARM with a decent set of peripherals, opensource compilerchain and opensource library. It has extensive debugging capabilities and most important its memory (both flash and SRAM) can grow without rewriting the code too much. If needed just pop in a different bigger chip and more memory is available.

Optimistically we called it BusPirate NextGen (NG for short). Ian still had the educational side of things in his scope and added a logic analyzer in the design. A second USB CDC endpoint was added to blast the logic analyzer data to the PC.

Unfortunately we run more or less into the same issues as we had with the Microchip controller: USB need regularly attention, which interferes with our interaction on the protocols, so we end up with stalls. Another big issue was that the peripherals were designed with moving data efficiently around and not in an educational way (as the BusPirate is ment to be). For example the I2C is nicely designed for reading memories or writing displays fast, but we need to know beforehand which byte is last. As we only can send a stop byte one or two bytes in advance of the stop bit. The design of the BusPirate menu system doesn’t cope with this properly (without major redesign).

Another major issues was the lack of a flexible way to connect a peripheral to a physical pin, like PPS on the Microchip microcontroller did. Because of the fixed pinout we ended up with a design that had upto 5 pins of the microcontroller connected together to an outside world pin. We did however finish the firmware into a more or less stable/usable version. For hystorical and for laugh it is in the git.

We dreamed about glueing a CPLD to all pins and design a switch matrix inside to emulate PPS so we had best of both worlds. A couple of beers and thinkering later we said why don’t we extend the idea. The flexiblility of a programmable logic chip to not only do the routing of signals, but also write the peripheral itself? This way we could ‘fix’ silicon errors like the I2C on the original BusPirate but also design the peripheral the way we want to address it as convenient as we want? This extra functionality would call for a FPGA because of the needed gates and some new skills to write the ‘software’ for it. We choose the ICE40 FPGA because of the opensource toolchain around it.

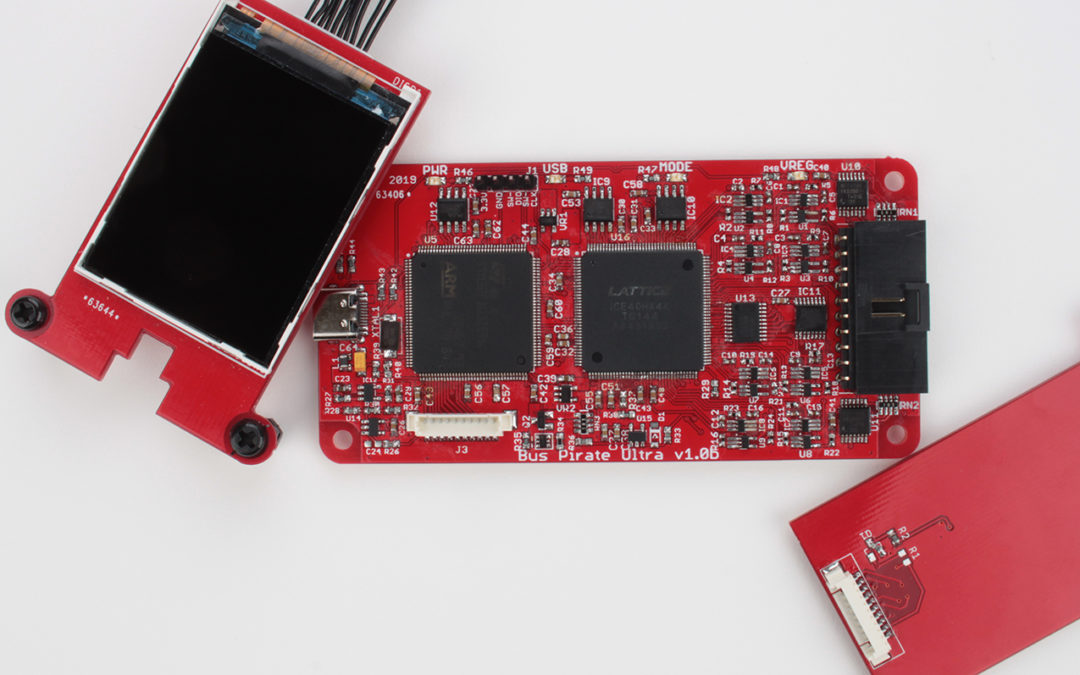

The design consist of an ARM chip (which acts a bit like the old USB to UART converter, albeit more intelligent) connected to the FPGA, has a builtin logic analyzer and ADC to monitor all IO pins on the header. Wack in a programmable power supply, selectable pullup resistors, solder-friendly and sturdy USB-C connector and a robust IO buffer and its good to be called the BusPirate Ultra. To make it over the top (optionally) we added a 2.2″ IPS TFT display to display all relevant data. Even more goodness is to come.

FPGA’s are nice an capable devices, but most of the modern ones cannot safely connect to 5V logic. Most stuff is nowadays 3V3 or lower, but we didn’t want to blow up a precious FPGA with its delicate IO pins. We designed a buffer that is capable of handling IO-levels from anywhere 1V8 upto 5V5. Also opendrain is supported for multidrop applications. The FPGA has enough IO pins to drive the buffers, add the logic analyzer and connection to the microcontroller (lots of IO pins to spare for future use). Now we got 8 pins capable of ’emulating’ any serial protocol, besides normal IO operations, PWM, frequency counter and servo interaction.

The interface between the microcontroller and FPGA is loosely based on interfacing SRAM. Larger STM32 chips have a FSMC (Flexible Static Memory Controller) in which a memory device (the FPGA in our case) is mapped into the memory space. There is a 16 bit wide data bus, 5 bit address bus and control-lines with access to all internals the way we want at lighting speed. Further things that we are adding or want to add:

- a programmable power supply

- programmable current protection

- arbitrary waveform generator..

The foto demonstrated an Ian-handsolder-friendly SC70 footprint. On the final (more or less) 4 layer design we gonna switch to a more PnP friendly footprint..

What do you need in the BusPirate Ultra?

Integrating JTAGulator-like functionality into the design would also be a really nice feature.